# CMPE - 310

Lecture 14 – Direct Memory Access Controller (8237)

# Outline

Direct Memory Access Controller :8237

- Pinout

- Operation

- Interfacing

# **Direct Memory Access (DMA)**

An alternative to the basic and interrupt-driven I/O discussed previously.

DMA allows data to be transferred between memory and the I/O device without processor intervention.

Speed of transfer limited to speed of memory components or DMA controller (up to 32-40 Mbytes/sec).

#### Common DMA operations:

- O DRAM refresh

- O Video refresh

- O Disk-memory system reads and writes.

Two signals are used to request/ack a DMA transfer:

O HOLD is an input to the micro that requests a DMA action.

O HLDA is an output from the micro granting the DMA action.

The microprocessor responds by suspending the execution of the program and by placing its address, data and control bus in high-impedance states.

# **Direct Memory Access (DMA)**

DMA 'reads' refer to transfers from memory to an I/O device and involves the use of MRDC and IOWC.

DMA 'writes' refer to transfers from an I/O device to memory and involves the use of MWTC and IORC.

The data transfer rate is determined by the speed of memory or the DMA controller (usually the latter).

The DMA controller provides memory with the address and select the appropriate I/O device (via DACK).

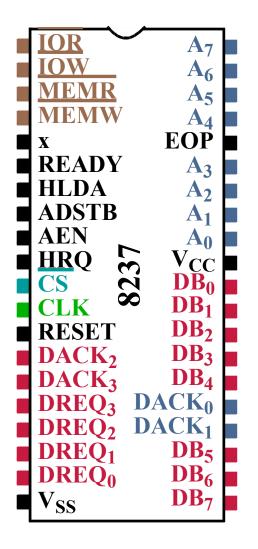

# DMA Controller: 8237

- $\circ$  Clk: < 5MHz.

- $O \overline{CS}$ : Output of a decoder.

- O RESET: Clears all internal registers (command, status, request, etc.).

- O READY: Allows memory and I/O to insert wait states into the 8237.

- O HLDA: Input that tells 8237 that micro has released address, data and control buses.

- O DREQ<sub>3</sub>-DREQ<sub>0</sub>: DMA request inputs used to request a DMA transfer.

- O  $DB_7$ - $DB_0$ : Used to program the 8237 and output upper 8-bits of address.

- O IOR, IOW, MEMR, MEMW: Outputs used to control memory and I/O.

- O  $\overline{\text{EOP}}$ : Bidirectional: as an input, used to terminate a DMA transfer, as an output, signals the end of the DMA transfer.

- A<sub>3</sub>-A<sub>0</sub>: Address pins select an internal register during programming and output part of the address for a transfer.

- O A<sub>7</sub>-A<sub>4</sub>: Address outputs.

- O HRQ: Output that connects to HOLD pin on micro to request a DMA.

- O DACK<sub>3</sub> DACK<sub>0</sub>: Used to select an I/O device (ack a DMA request).

- O AEN/ADSTB: Enable latch (and strobe) to transfer  $DB_x$  to upper 8 A bits.

### DMA Controller: 8237

Some of the internal registers are:

- CAR<sub>3</sub> CAR<sub>0</sub>: Used to hold the 16-bit memory address used for a DMA transfer. Either incremented or decremented after a byte is transferred.

- O CWCR<sub>3</sub> CWCR<sub>0</sub>: Current word count register programs a channel for the # of bytes (up to 64KB) transferred during a DMA action.

- O CR: Command register programs the operation of the 8237. Bits in this register allow: Memory-to-memory transfers (like MOVSB) where DMA channel 0 holds the source address and DMA channel 1 holds the dest address.

Memory-to-memory transfers in which DMA channel 0 holds a constant address -- used to fill a memory regions with a constant.

Fixed or rotating DMA channel priority, plus misc other options.

- O MR: 'Mode of operation' register -- one for each channel. For example, block mode is used for memory-to-memory transfers.

- O RR: Request register is used to request a DMA transfer via software -- essential for processor initiated memory-to-memory transfers.

- O SR: Status register indicates when a DMA has completed.

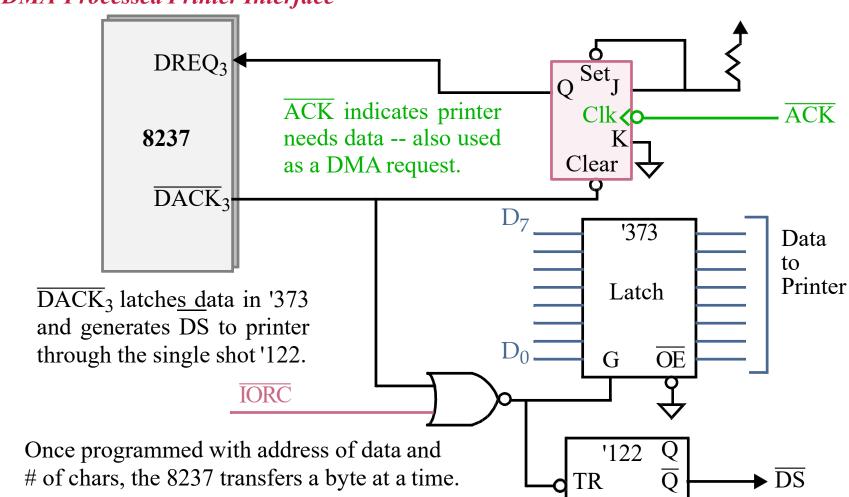

**DMA-Processed Printer Interface**

Note that the I/O device is NOT selected by decoding the address bus, but rather by

DACK, since address bus contains a memory address.

See code in book and example of 8237 connected to an 8088.