# **CMPE-310**

# Lecture-02: 8086 Architecture

#### Outline

Basic Architecture Bus Types Bus Standards Bus Architecture Memory Bank Layouts Basic I/O Architectures Interrupt Vectors I/O Space

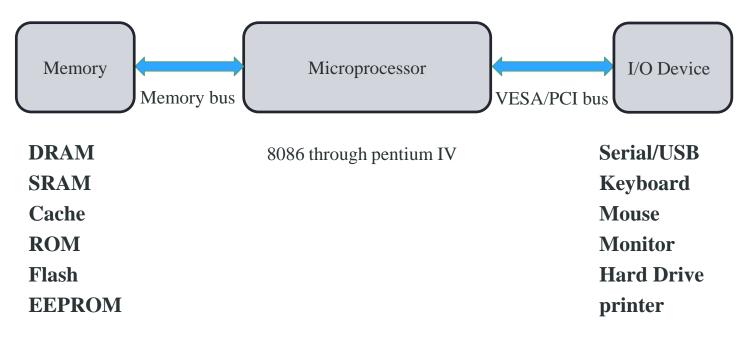

#### **Basic Architecture**

#### **Basic Components**

## **Bus Types**

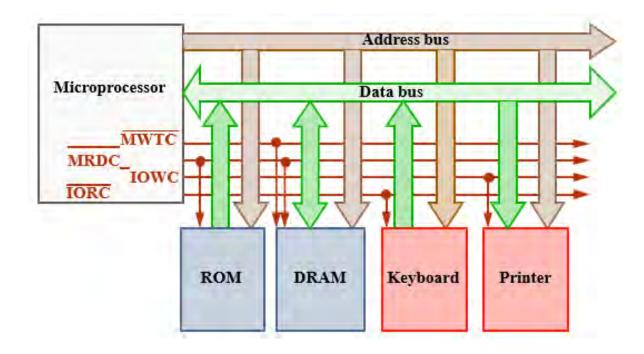

Address Bus : Computer bus (a series of lines/wires connecting two or more devices) that is used to specify a physical address.

Data Bus : Provides for transportation of data.

**Control Bus :** CPU transmits a variety of control signals to components and devices using the control bus. Most systems have at least 4 control bus connections (active low). *MRDC* (Memory ReaD Control), *MWRC*, *IORC* (I/O Read Control), *IOWC*.

| 20  | 1         |

|-----|-----------|

| 21  | 2         |

| 22  | 4         |

| 23  | 8         |

| 24  | 16        |

| 25  | 32        |

| 26  | 64        |

| 27  | 128       |

| 28  | 256       |

| 29  | 512       |

| 210 | 1024~= 1K |

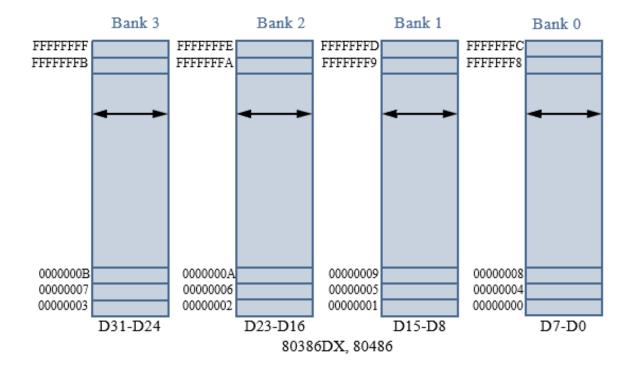

### Intel family of microprocessor bus and memory sizes

| Microprocessor                                           | Data Bus Width | Address Bus Width | Memory Size |

|----------------------------------------------------------|----------------|-------------------|-------------|

| 8086                                                     | 16             | 20                | 1M          |

| 8088                                                     | 8              | 20                | 1M          |

| 80186                                                    | 16             | 20                | 1M          |

| 80188                                                    | 8              | 20                | 1M          |

| 80286                                                    | 16             | 24                | 16M         |

| 80386SX                                                  | 16             | 24                | 16M         |

| 80386DX                                                  | 32             | 32                | 4G          |

| 80386EX                                                  | 16             | 26                | 64M         |

| 80486                                                    | 32             | 32                | 4G          |

| Pentium                                                  | 64             | 32                | 4G          |

| Pentium Pro-Core2                                        | 64             | 32                | 4G          |

| Pentium Pro-Core2<br>(if extended addressing is enabled) | 64             | 36                | 64G         |

| Pentium 4 and Core2<br>with 64-bit extensions enabled    | 64             | 40                | 1T          |

| Itanium                                                  | 128            | 40                | 1T          |

#### **Bus Architecture**

#### **Bus Standards**

ISA (Industry Standard Architecture): 8 MHz, 8-bit (8086/8088) 16-bit (80286-Pentium)

EISA (Enhanced Industry Standard Architecture): 8 MHz, 32-bit (older 386 and 486 machines).

*PCI (Peripheral Component Interconnect)*: 33 MHz, 32-bit or 64-bit (Pentiums), New: PCI Express and PCI-X 533 MTS

*VESA (Video Electronic Standards Association)*: Runs at processor speed (32-bit or 64-bit Pentiums) Only disk and video.

Competes with the PCI but is not popular.

#### **Bus Standards**

USB (Universal Serial Bus): 1.5 Mbps,12 Mbps, USB 2.0 - 480 Mbps and USB 3.2 upto 20 Gb/s.E.g. keyboards, mouse, modems and sound cards.Introduced to reduce system cost through fewer wires

AGP (Advanced Graphics Port): 66MHz. (PCIE v6.0 is current standard – 128 GB/s)

Fast parallel connection: Across 64-bits for 533 MB/sec.

E.g. video cards.

To accommodate DVD (Digital Versatile Disk) players. AGP 3.5 had peak bandwidth of 2.1GB/s.

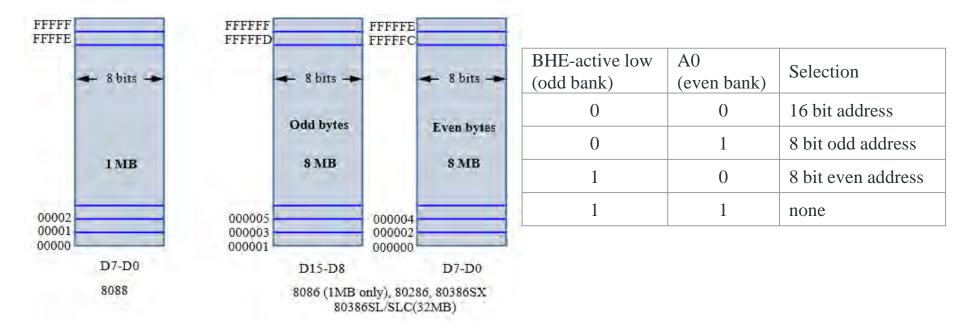

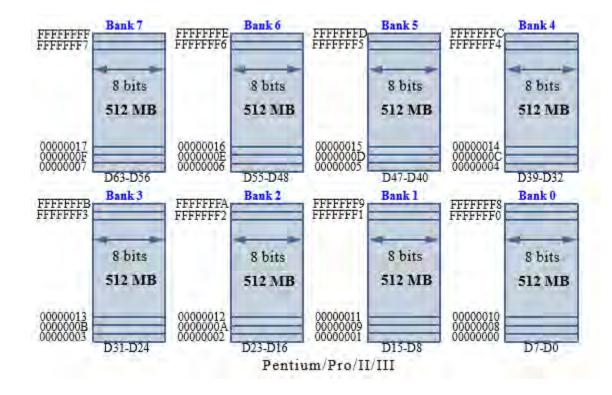

8086 processor

20-bit addressing model. Natural word size – 2 bytes.

Two banks (physically separate chips/modules) allow simultaneous access to two bytes. No need for separate memory controller.

Why not use a single chip?

Modern processors access memory in chunks. Memory latency didn't matter back in the 1970s. CPU was too slow and memory modules were manufactured 8-bit wide.

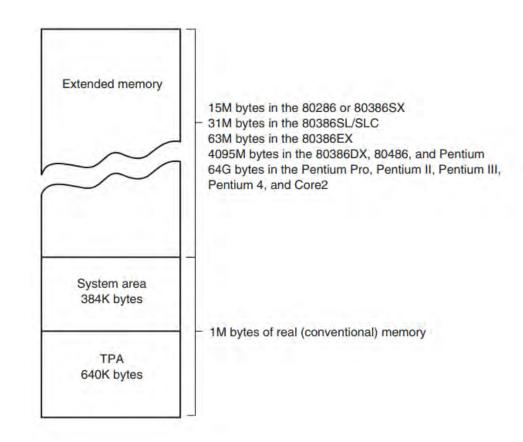

# **Memory Map**

Transient program area (TPA) holds the DOS (disk operating system) operating system and other programs that control the computer system.

System area contains programs for system communication (peripherals).

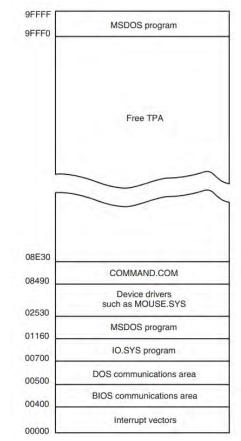

# **Inside the TPA**

Interrupt vectors access various features of the DOS, BIOS (basic I/O system), and applications.

BIOS is a collection of programs stored in either a read-only (ROM) or flash memory that operates many of the I/O devices connected to your computer system.

BIOS and DOS communications areas contain transient data used by programs to access I/O devices and the internal features of the computer system.

IO.SYS is a program that loads into the TPA from the disk whenever an MSDOS system starts up.

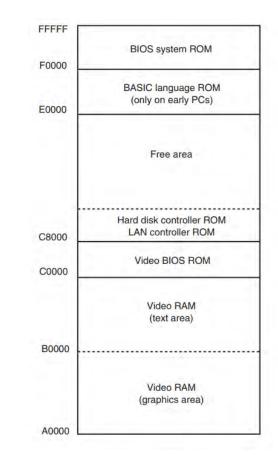

### **Inside the System Area**

Contains programs on either a read-only memory (ROM) or flash memory, and areas of read/write (RAM) memory for data storage.

Video, LAN BIOS, Hard disk controller drivers and other programs.

# **I/O Space**

NOT memory mapped on 80x86

| I/O Device Space      |                        | FFFF   |

|-----------------------|------------------------|--------|

|                       | • I/O Expansic         | n Area |

| 64K 8-bit I/O devices | COM1                   | 03F8   |

|                       | Floppy Disk Controller | 03F0   |

|                       | CGA Adapter            | 03D0   |

|                       | LPT1                   | 0378   |

|                       | Hard Disk Controller   | 0320   |

|                       | COM2                   | 02F8   |

|                       | 8255 (PIA)             | 0060   |

|                       | Timer (8253)           | 0040   |

|                       | Interrupt Controller   | 0020   |

|                       | DMA Controller         | 0000   |

Special instructions, IN/OUT to communicate with I/O devices